前言

本来想把和IR Drop 相关的封装内容一篇写完,结果发现难度有点大。首先,写一篇很费时间,其次,一篇写完,大部分人也没有耐心读完。那就分开写吧,一篇写一个点(适合快速阅读,也顺便了解一个知识点)。刚入行的小伙伴都经历过这些专业名词,def,spf,sdf等,当时各种傻傻的分不清,应该有些人工作几年也不一定知道这些文件里面的格式和主要内容。本篇和后面几篇将要介绍的是CPA,CPM,CTM,不知道你是否分的清?本篇首先介绍CPA.

CPA(Chip Package Analysis)

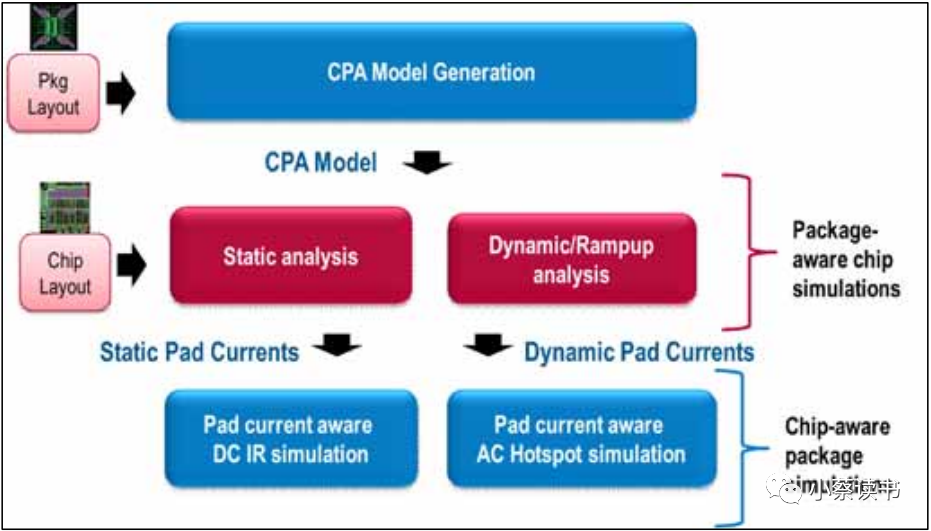

如下图所示,CPA model是Pkg Layout(封装基板设计)通过工具提取出来的一个模型,主要包括封装基板中的RLC参数。CPA可以提供每个bump的寄生参数,可以用来做chip+package的协同仿真。

chip+package可以做static分析,仿真可以得到每个pad的电流,可以为pad的过流能力是否超标做参考,这种方式属于直流仿真;当做dynamic仿真时,属于交流仿真。

问题

1.在抽取CPA model时,根据pin group不同,可以分为Lumped Grouping/Group by Each Pin/Group by X-Y Grid三种方式,这三种方式IR结果相差比较大,每个公司根据自己的经验选取方式不统一。Lumped Grouping所有pin一起抽,IR最小;Group by Each Pin 每个pin单独抽,IR最大,但是工具计算量大,run time长;Group by X-Y Grid 介于两者之间。

2.带CPA和不带CPA仿真,结果相差大吗?Static IR相差不大,Dynamic IR相差较大(尤其翻转率高的地方),为啥呢?自己思考下.

3.封装上的走线不均匀,连接弱的地方IR会比较大。另外GUI界面可以看到每个bump的电阻和电感。

讨论

1.你在工作中还遇到过哪些跟CPA相关的IR问题?欢迎一起讨论.

参看文献:

《RedHawk User Manual》