TCD CELL

TCD:Test-key Critical Dimension.在半导体制造过程中,可以实现的最小线宽称为关键尺寸(Critical Dimension)。在越小的尺寸中,关键尺寸越需要好的均一性。因为好的均一性对器件的电学特性(阈值电压、漏电流等等)影响很大。TCD就是为了监控芯片上关键尺寸变化做的一些测试结构。一般应用用40nm以下,2000um放一个。

CLAMP CELL

(1)分类

CLMAP CELL根据使用地方分为core区域的clamp cell和I/O区域clamp cell (电压不同);根据方向分为垂直和水平方向(根据floorplan 选择)。

(2)电路结构及工作原理

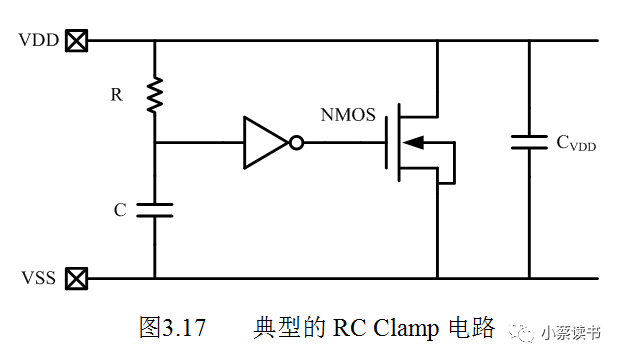

典型的RC Clamp钳位电路如图3.17所示(实际应用中反相器为三级),在ESD事件发生时他们可以提供一条额外的分流路径。这些瞬态钳位利用了ESD脉冲快速的dv/dt,通过电容耦合电荷到内部控制节点。这个节点的电压或者电荷被用来触发电路,比如一个晶体管,对于ESD脉冲提供一条从电源到地泄放通道。最终,控制节点通过电阻R泄放,钳位管关闭。这种方法的缺点是在电源正常上电的过程有限的噪声免疫力和钳位管电势。对于HBM ESD应力大约600-750ns,为了设计合适的RC电路,RC时间常数必须设计大于1ms来触发钳位管,保持在整个ESD事件过程中钳位管处于导通状态。为了满足这个标准,R通常用50kΩ的N阱电阻实现,C用20pF NMOS晶体管poly栅电容实现。时间常数需要的大电阻和电容占很大的面积。应当仔细仿真电源线最大电容和耦合电容,因为这些电容可能影响钳位管的触发效率。这是因为ESD事件不仅给控制电路电容充电,也给寄生电容充电。结果是,ESD钳位管的开启时间增加。

(3)clamp cell 电阻限制

一般对clamp cell摆放约束时电源线和底线的电阻要小于0.1欧姆。为什么有这个要求?

因为考虑了VDD和VSS电源线的寄生的杂散电阻和电容之后,全芯片的ESD保护效果可能并不理想。ESD放电在很短的时间内就会达到数安培的放电电流,如果VDD和VSS电源线之间的钳位单元距离ESD注入的输入或者输出管脚位置太远,ESD电流就不能得到及时的泄放,也就是虽然有VDD和VSS电源线之间的钳位单元,由于摆放位置的不合理性,内部电路还是会出现损伤。

下面通过实验数据来看距离对ESD泄放能力的影响。

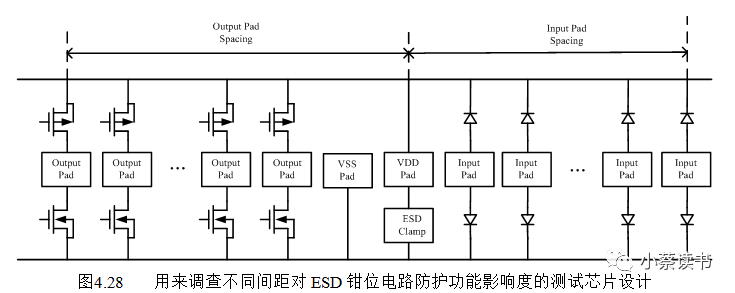

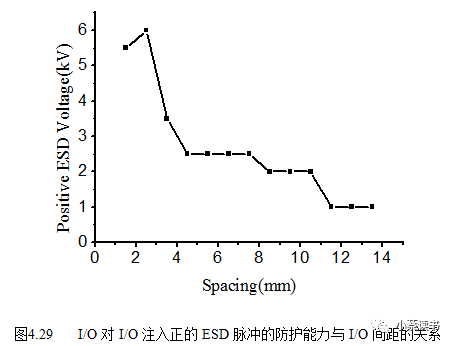

图4.28显示了该实验的布局设计,连接输入/输出脚与VDD PAD的是宽30μm的电源线,连接输入/输出脚与VSS PAD的也是宽30μm的电源线。该实验芯片流片工艺采用0.8μm标准CMOS工艺,管脚与管脚之间的ESD耐压特性如图4.29所示,当两个管脚相隔越远时,其ESD耐压能力越低。

从图4.29可以看出,随着输入/输出管脚和钳位单元距离的增加,ESD的耐压能力下降了很多,这表明电源线上的杂散电容/电阻对全芯片ESD保护能力的负面影响很大。为了使电源线上的寄生电容/电阻对ESD防护能力影响满足设计要求,电源线的尺寸以及钳位单元的摆放位置都必须满足一定的要求。