点击上方蓝字关注我们

“如果CPU爱好哲学,他可能一直会问自己两个问题,我要运算的数据从哪里来,我运算完的数据又到哪里去了“,这两个问题就跟存储器有关。

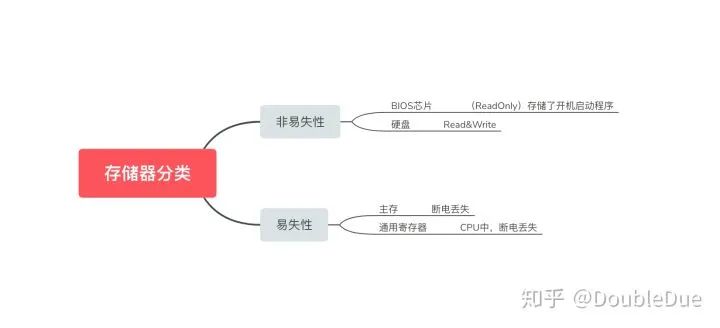

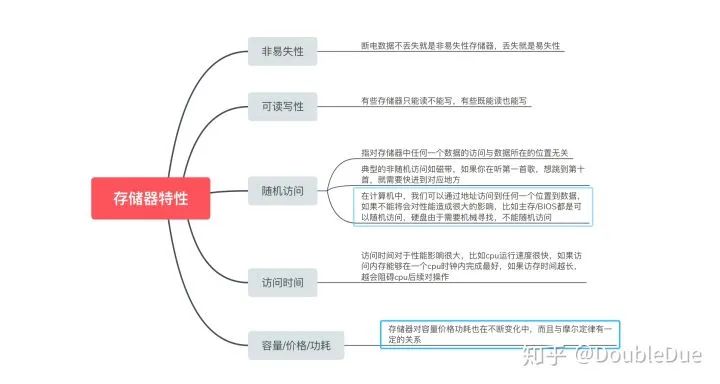

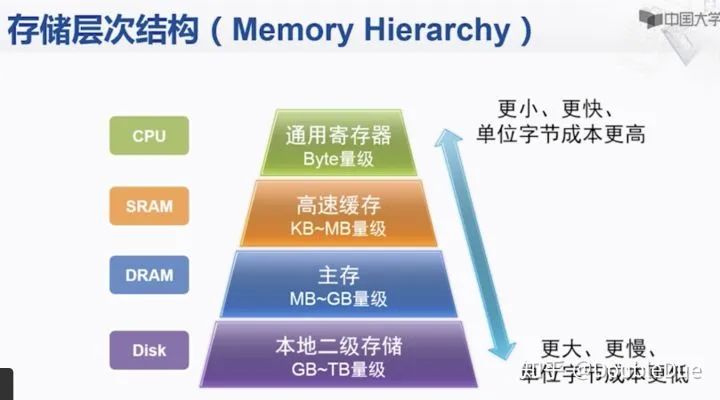

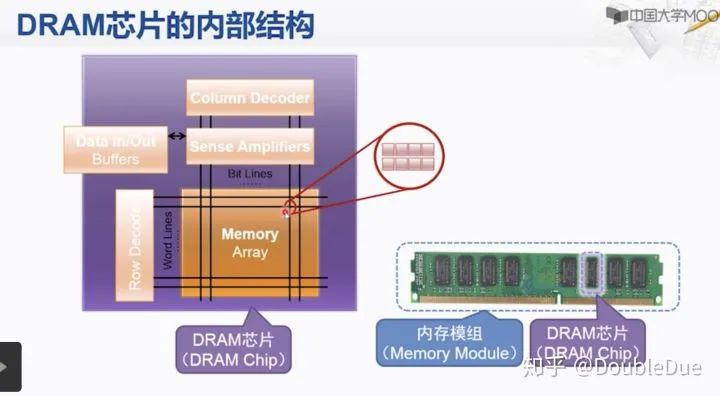

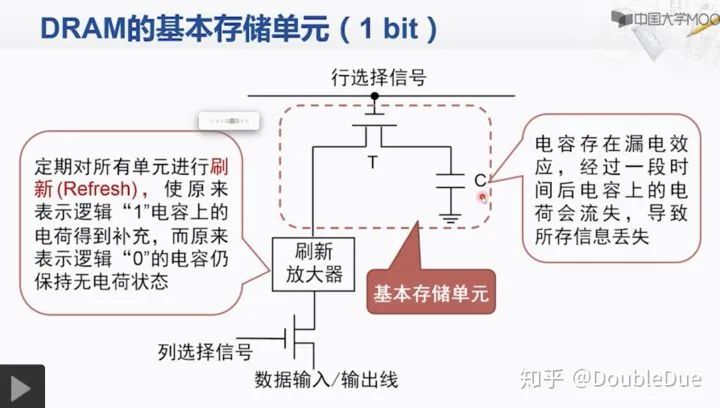

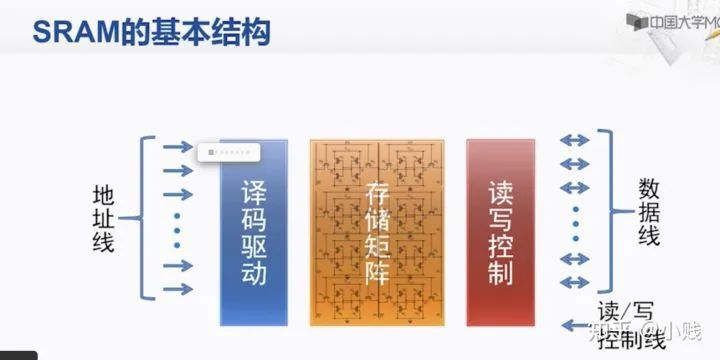

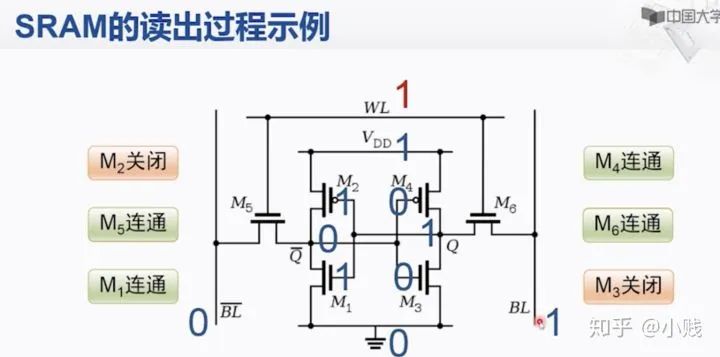

存储器在计算机中分为易失性和非易失性两种,分别对应了冯诺伊曼体系结构中的一些部件; 存储器追踪到根儿是通过容器充放电或者晶体管来存储1/0信息以达到存储信息的功能的

●

深入浅出大数据组件之Kafka消息队列 DLab数据实验室,公众号:DLab数据实验室深入浅出大数据组件之Kafka消息队列

●

实时数据流计算引擎Flink和Spark剖析 小舰,公众号:DLab数据实验室实时数据流计算引擎Flink和Spark剖析

长按二维码识别关注

文章都看完了 不点个

不点个 吗

吗

文章转载自DLab数据实验室,如果涉嫌侵权,请发送邮件至:contact@modb.pro进行举报,并提供相关证据,一经查实,墨天轮将立刻删除相关内容。