组成计算机的三大件是CPU、内存和IO。CPU和内存就不用说了,那么IO具体是什么呢?

IO就是IN和OUT的简称。这个IN和OUT是相对的,比如CPU需要从内存中提取数据来运算,运算完后再放回内存,或者直接将电信号发向一些针脚以操作外部设备。对于CPU来说,从内存提取数据,就叫做IN。运算完后将数据直接发送到某些其他针脚或者放回内存,这个过程就是OUT。对于磁盘来说,IN是指数据写入磁盘的过程,OUT则是指数据从磁盘读出来的过程。

IO只是一个过程,数据在每个部件中不断地进行IO过程,传递给CPU由其进行运算处理之后,再经过IO过程,最终到达输出设备供人使用。

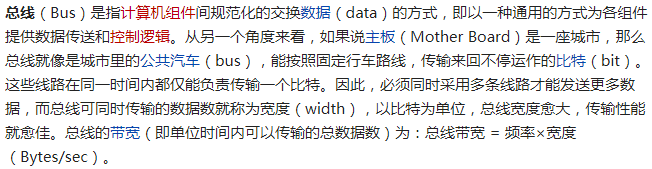

IO的通路——总线

来自维基百科

现代计算机中,IO是通过共享一条总线的方式来实现的。总线也就是一条或者多条物理上的导线,每个部件都接到这些导线上,导线上的电位每个时刻都是相等的,这样总线上的所有部件都会收到相同的信号。也就是说,这条总线是共享的,同一时刻只能有一个部件在接收或者发送,是半双工的工作模式。

关于半双工工作模式:

一共有三种工作模式,单工、半双工、全双工

单工数据传输只支持数据在一个方向上传输;半双工数据传输允许数据在两个方向上传输,但是,在某一时刻,只允许数据在一个方向上传输,它实际上是一种切换方向的单工通信;全双工数据通信允许数据同时在两个方向上传输,因此,全双工通信是两个单工通信方式的结合,它要求发送设备和接收设备都有独立的接收和发送能力。

所有部件按照另一条总线,也就是仲裁总线或者中断总线上给出的信号来判断这个时刻总线可以由哪个部件来使用。产生仲裁总线或者中断电位的可以是CPU,也可以是总线上的其他设备。如果CPU要向某个设备做输出操作,那么就由CPU主动做中断。如果某个设备请求向CPU发送信号,则由这个设备来主动产生中断信号来通知CPU。CPU运行操作系统内核的设备管理程序,从而产生了这些信号。

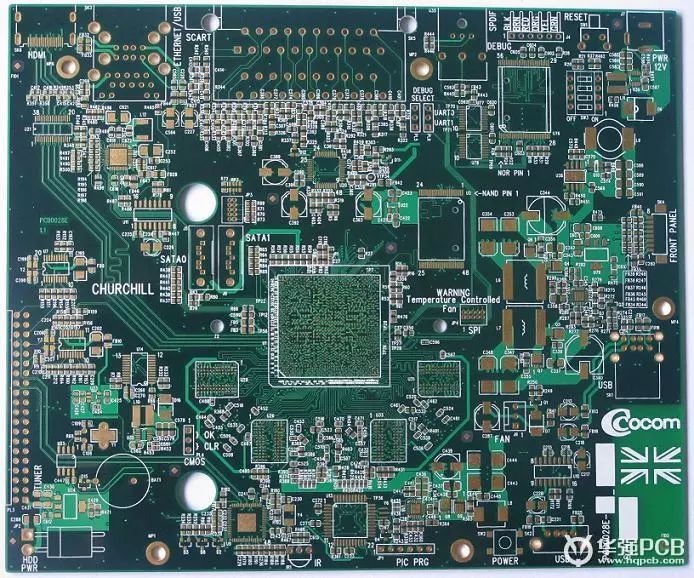

主板上的每个部件都是通过总线连接起来的。实际中,导线的数目可能是8条,可能是16条、32条、64条甚至128条。这些导线密密麻麻地印刷在电路板上,由于导线之间非常密集,在高频振荡时会产生很大干扰,所以人们将这些导线分组印刷到不同电路板上,然后再将这些电路板压合起来,形成一块板,这就是多层印刷电路板(多层PCB)。

这样,每张板上的导线数量降低了,同时板与板之间的信号屏蔽性很好,不会相互干扰。这些导线之中,有一些是部件之间交互数据用的数据总线,有些则是它们互相传递控制信号用的控制总线,有些则是中断与仲裁用的中断总线,还有一些则是地址总线,用来确认通信时的目标设备。

来自维基百科

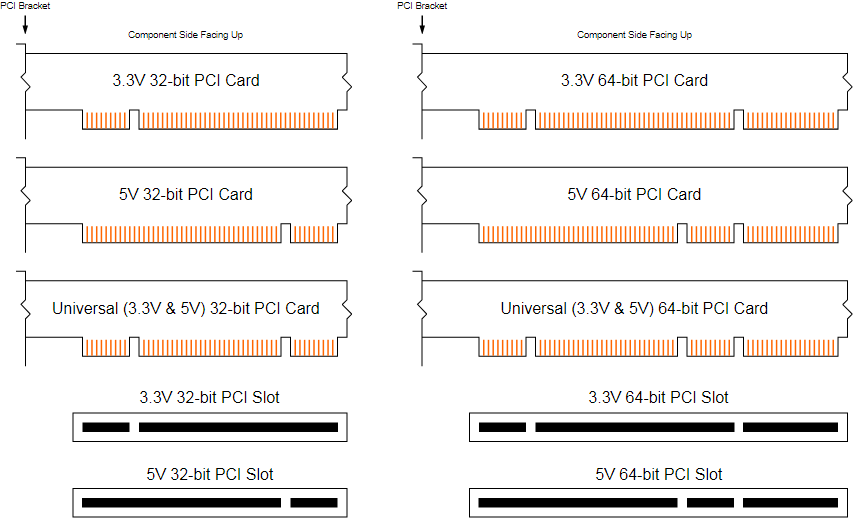

一般按照数据总线的条数来确认一个总线或设备的位宽(CPU是按照其内部寄存器到运算单元之间的总线数目来确定位数的)。比如32位PCI总线,则表明这条总线共有32根导线用于传递数据信号。PCI总线可以终结在一个插槽,用于将PCI接口的板卡接入PCI总线,也可以直接与设备连接。后者一般用于集成在主板上的设备,因为它们之间无须使用插槽来连接。

32位&64位PCI卡

目前最新的主板架构中,高速总线比如PCIE 2.0往往是直接接入北桥,南桥只连接低速总线

来自维基百科

PCI总线

PCI总线是目前台式机与服务器所普遍使用的一种南桥与外设连接的总线技术。

来自维基百科

PCI总线的地址总线与数据总线是分时复用的。这样的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在数据传输时,一个PCI设备作为发起者(主控,Initiator或Master),而另一个PCI设备作为目标(从设备、Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#信号Master用来请求总线使用权的信号,当得到仲裁器(Arbiter)的许可时(GNT#信号),会将FRAME#信号(传输开始或者结束信号)置低,并在地址总线(也就是数据总线,地址线和数据线是共享的)上放置Slave地址,同时C/BE#(命令信号)放置命令信号,说明接下来的传输类型。

所有PCI总线上的设备都需对此地址译码,被选中的设备要置DEVSEL#(被选中信号)以声明自己被选中。当IRDY#(Master可以发送数据)与TRDY#(Slave可以发送数据)都置低时,可以传输数据。

当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

PCI总线的中断共享

PCI总线可以实现中断共享,即不同的设备使用同一个中断而不发生冲突。硬件上,采用电平触发的办法:中断信号在系统一侧用电阻接高,而要产生中断的板卡上利用三极管的集电极将信号拉低。这样不管有几块板产生中断,中断信号都是低电平;而只有当所有板卡的中断都得到处理后,中断信号才会恢复高电平。

软件上,采用中断链的方法:假设系统启动时,发现板卡A用了中断7,就会将中断7对应的内存区指向A卡对应的中断服务程序入口ISR_A;然后系统发现板卡B也用中断7,这时就会将中断7对应的内存区指向ISR_B,同时将ISR_B的结束指向ISR_A。依此类推,就会形成一个中断链。而当有中断发生时,系统跳转到中断7对应的内存,也就是ISR_B。ISR_B就要检查是不是B卡的中断,如果是则处理,并将板卡上的拉低电路放开;如果不是则呼叫ISR_A。这样就完成了中断的共享。