精彩导读

Perl和Tcl是ic设计中最常用的两种脚本语言,在这里先总结一下Perl的作用:

用于生成Verilog代码

在写verilog时,经常遇到一些规律性强,编写又比较麻烦的代码,而这些恰恰又是可重用性比较强的。比如总线模块、FIR滤波器、IIR滤波器,只要滤波器阶数和参数定了编码都大致相似的模块,就比较适合用来自动生成实现他们功能的verilog代码。Perl的强项在于文本处理,对于verilog代码的生成,perl的代码会比较简洁易写。

用于扩充Verilog的语法

有一些verilog没有的语法功能,可以使用perl来扩充。比如工程中某变量的bit数有变化,导致了门级描述中门的个数变化,就可以用perl来生成相应的verilog代码。

用于验证中的数据处理

验证中有些数据格式需要处理,还有些数据需要分析。比如用matlab生成的数据改写成verilog能识别的ROM格式,或是直接生成ROM的verilog。还有Verilog验证后生成的数据格式变成下一级做数据分析软件能识别的格式。Perl还能直接对verilog验证所得数据进行数据比对和分析。

后端工具与前后级连接的格式处理

如果说Tcl比较常用在后端的软件使用中,那么perl就大多数用在软件和软件之间粘合上。有一些前级的工具所得结果不能直接用于下级工具的输入,那他们之间的转换用perl是完全合适的。

如上所述,基本上都用在文本格式的转换上。其实,perl的功能和C/C++是一样的,只是运行的方式不同,C等是编译之后生成exe文件,而perl是需要perl的运行环境支撑,有点像运行语句编译一句的感觉,这就与matlab的原理有点相似。可perl与C相比更加灵活,在文本操作上的编码相当简便。

脚本语言也是IC工程师必须要掌握的技能。

手稿解读

问:

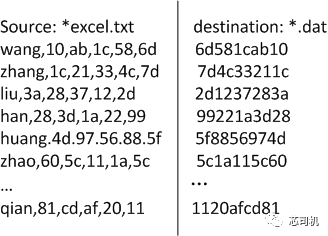

用perl或者shell脚本对当前目录中所有符合下面名字的文件内容进行处理,并同意第一列每个单词出现的个数,左图为源文件,右图为处理后的文件。

答:

open INF, "excel.txt";

my $line = <INF>;

my $string_num; #统计单词出现的次数

while (defined $line) {

if ($line =~/^[a-z]+,(\w\w),(\w\w),(\w\w),(\w\w),(\w\w)$/) {

print "$5$4$3$2$1\n";

$string_num = $string_num + 1;

} else {

print "$line";

}

$line = <INF>;

}

close <INF>;

PS: 分享朋友圈,截图并回复微信公众后台,你可以得到详细源代码。

往期真题

PS:已有公司参考芯司机真题作为笔试面试题(同时希望各位同学共享笔试面试题到微信号:eecourse)

《每日一题》第4题-谈谈对静态时序分析、动态时序仿真的理解及优缺点

《每日一题》第5题-谈谈对FPGA和ASIC的理解,各自的特点

《每日一题》第6题-如何理解 Setup time 和 Hold time?

《每日一题》第7题-为什么DFF有Setup time和Hold time的要求

《每日一题》第10题-名词解释 算法篇

《每日一题》第12题-名词解释 存储篇

《每日一题》第13题-名词解释 设计流程篇

《每日一题》第15题-名词解释 何为同步复位和异步复位?何为异步复位、同步释放?

《每日一题》第19题-SoC芯片验证包括哪些内容,各自的目的是什么?

《每日一题》第21题-画出CMOS 非门/与非门/或非门的结构

《每日一题》第22题-用两输入或非门实现如下逻辑?B=en?Mask&A:A

《每日一题》第24题-BC-WC、OCV、AOCV分析的对比

《每日一题》第27题-谈谈Spare Cell 在芯片设计中的作用

《每日一题》第30题-画出AHB INCR4 burst 读写传输时序图,INCR4/WRAP4区别

《每日一题》第33题-何为时序路径,请画出下图电路中的时序路径

《每日一题》第38题-谈谈对ESD的理解以及芯片需要在哪些地方插入ESD保护结构?

《每日一题》第40题-谈谈芯片的IO排布形式,与封装之间的关系?

《每日一题》第42题-谈谈对Multi cycle path的理解?

《每日一题》第46题强化一下CG(clock gating) cell的使用

《每日一题》第50题FPGA芯片中的储存器资源

《每日一题》第63题低功耗设计:level shifter/isolation cell

《每日一题》第67题timing:OCV下如何计算timing(更正和扩展版)

《每日一题》第71题时钟树:stop pin,exclude pin,float pin

《每日一题》第80题DFT:fault simualtion

直击求职难点,真题秀,剑指offer

请大家持续关注芯司机,我们会带来更多更全面的知识分享,助力学生就业,打造好就业加油站平台