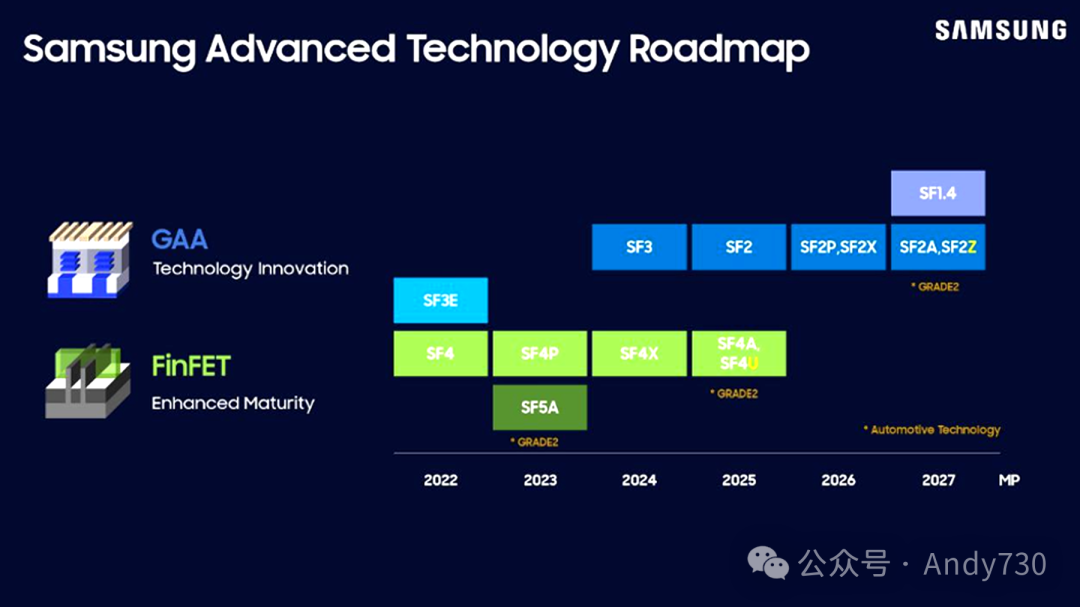

三星在一场以“推动AI革命”为核心的行业Foundry活动中,宣布了全新的工艺节点和技术进展,并发布了直至2027年的技术路线图(详见下文)。

三星半导体光刻节点路线图

三星半导体光刻节点路线图

三星特别推出了两个新的工艺节点:SF2Z和SF4U。其中,2纳米的SF2Z集成了背面供电网络(BSPDN),旨在消除电源与信号线之间的干扰。与SF2(三星首款2纳米节点)相比,SF2Z不仅提升了功率、性能和面积(PPA),还减少了IR降(即导体在电流流动过程中两端的电压降),从而显著增强了高性能计算设计。该新节点预计将于2027年开始大规模生产。而SF4U节点则通过提升PPA进行改进,计划于2025年开始大规模生产。

三星还计划于2027年开始大规模生产SF1.4(1.4纳米)产品。该公司表示,进一步缩小至1.4纳米以下将需要材料和结构上的创新。自2022年起,三星已开始生产GAA CMOS,并计划在未来推出的2纳米工艺中采用该技术。

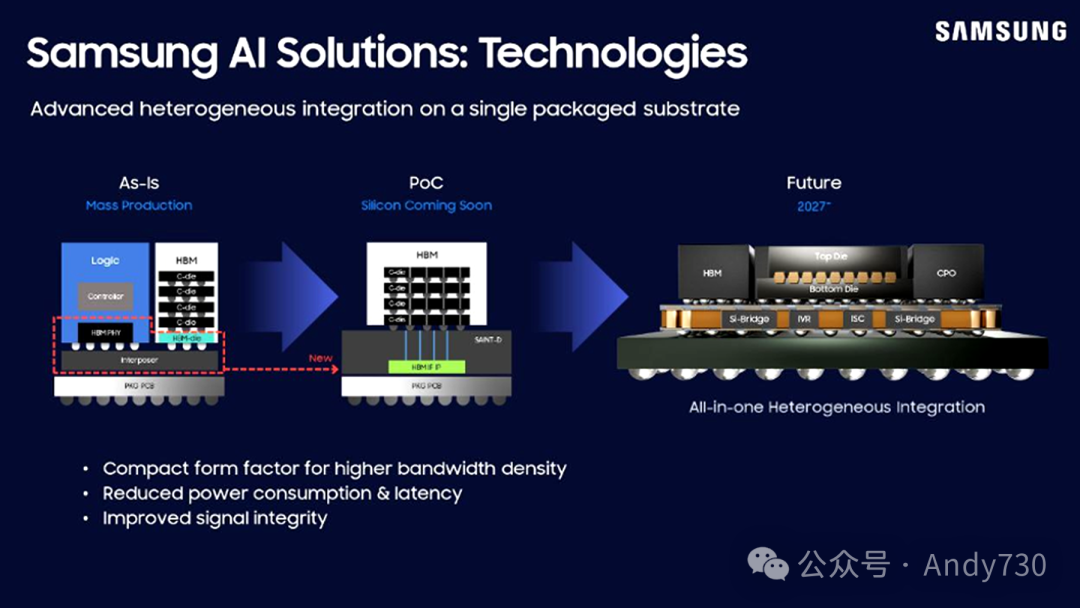

三星的AI Foundry解决方案(如下图所示)采用了全环绕门(GAA,Gate All Around)CMOS工艺,提供低功耗AI芯片。然而,如右图所示,该公司还计划在2027年将共封装光学(CPO,Co-Packaged Optics)引入Chiplet架构中,以进一步提升性能。

三星的Foundry封装计划

三星的Foundry封装计划

该公司表示,其三星Foundry AI销售在过去一年增长了80%。除了领先的工艺节点外,三星还提供专用和8英寸晶圆产品,以满足汽车、医疗、可穿戴设备和物联网应用等领域的客户需求。据了解,三星Foundry业务中的几款产品包括MRAM等新兴存储器,这些存储器被广泛应用于可穿戴设备和其他AI推理应用中。

在2023年的Foundry活动中,三星推出了其多芯片集成联盟(Multi-Die Integration Alliance)。这是一种创新的Chiplet集成形式,主要通过将单一用途的芯片组合在高性能封装中,实现各种Chiplet(包括来自不同芯片供应商的组件)的灵活组合,从而形成一个完整的工作系统。三星表示,这一战略将重点关注2.5D和3D IC设计。值得注意的是,三星于2022年与英特尔等众多公司合作,推出了UCIe Chiplet架构。UCIe基于CXL架构,为内存扩展和池化提供了强有力的支持。

除了Foundry业务外,三星在DRAM和NAND闪存领域也占据市场领先地位。该公司于2022年推出了行业首款CXL内存(512GB),并在2023年初推出了首款LPCAMM2 DRAM和首款GDDR7 DRAM。特别是在高带宽内存(HBM)模块中,DRAM是AI处理包(如NVIDIA所构建的包)中的关键组成部分。三星在公告中特别展示了其HBM模块。

此外,三星与其他Foundry厂商正致力于提供非易失性存储器方案,以取代在先进制造节点下无法扩展的NOR闪存(NOR闪存在28纳米以下无法扩展),并用于替换一些高级缓存SRAM以存储AI推理模型(因为MRAM单元是非易失性的,且占用较少的芯片面积)。

迄今为止,已有产品采用MRAM取代了NOR,但ReRAM也是一种可行的选择。Chiplet架构和3D异构集成将整合更广泛的存储器和其他组件,以满足专业应用的需求。

在三星的论坛活动以及随后的SAFE和MDI联盟研讨会上,该公司不仅扩展了其2纳米和4纳米产品线,还宣布了到2027年将包括共封装光学在内的Chiplet集成计划,并强调了其AI Foundry业务在过去一年实现了80%的增长。

Source:Tom Coughlin; Samsung Shows New Nodes And Chiplet And 3D Integration Plans; Jun 14, 2024

--【本文完】---

近期受欢迎的文章:

更多交流,可添加本人微信

(请附姓名/单位/关注领域)