上文讲到了一位加法器的原理,这次,我们来实现多位加法器。

同样,我们只关注逻辑,不关注具体电路、元件。

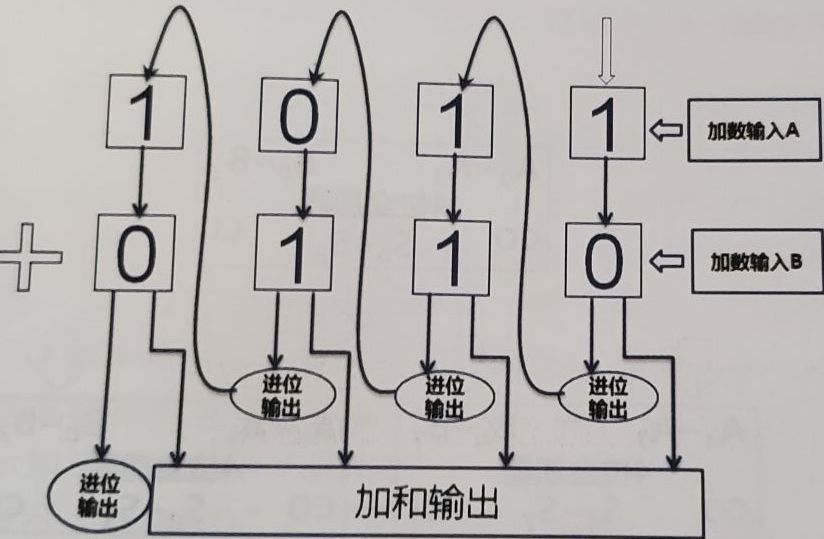

多位二进制数的运算

二进制数的加法与我们数值的十进制数加法无太大区别:按位相加,进位;处理含进位的按位相加时,先进性两个操作数的按位相加,然后用本位留下的数与进位相加(想想便可知:这两次相加最多会出现一次进位。)

因此,逻辑电路实现如下功能即可:

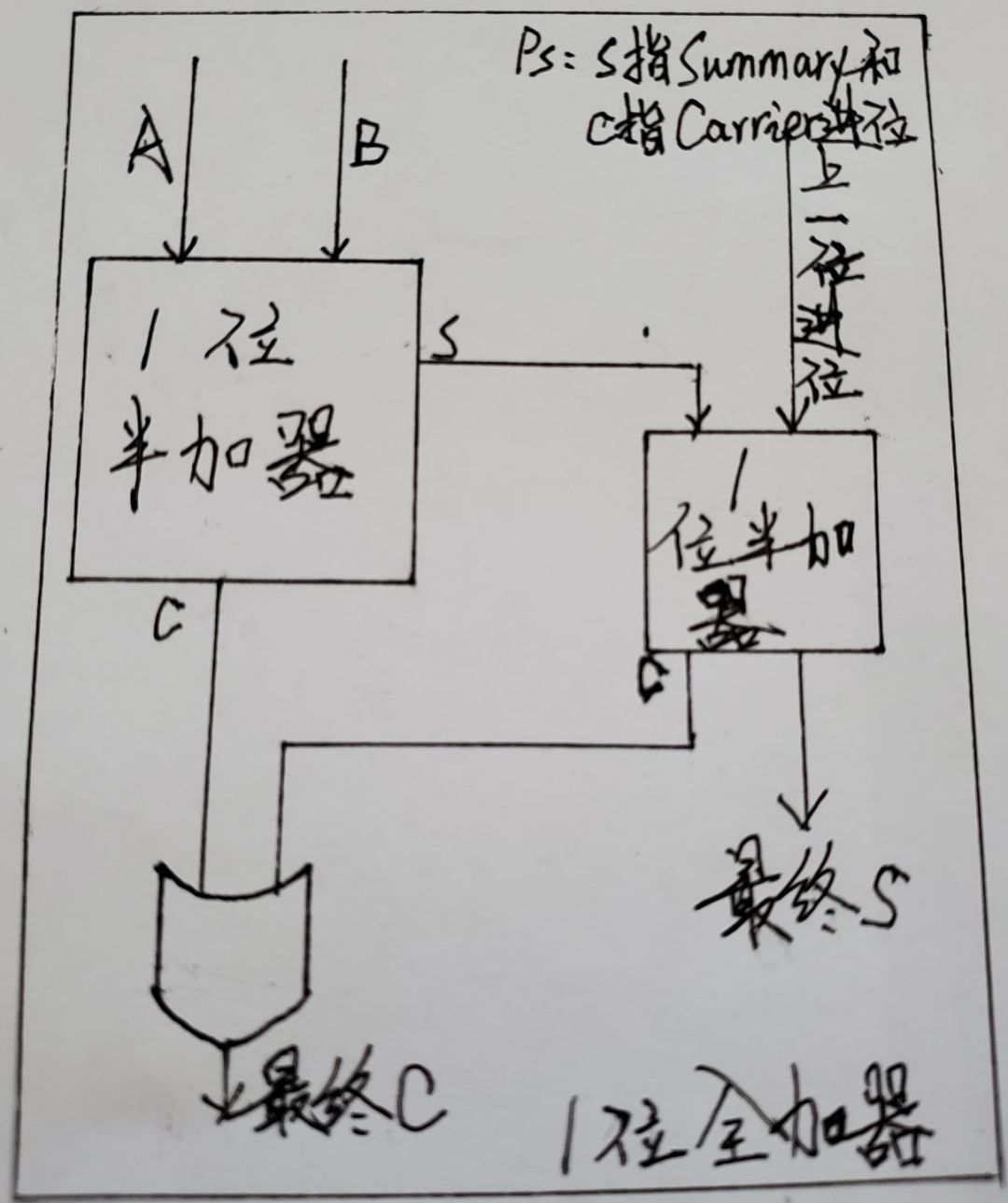

考虑上一位的进位:半加器得到的加法值与上一位的进位值进行异或运算,得到该位的最终值,用半加器的加法值与上一位进位值进行与运算得到一个值,再用这个值与半加器的进位值进行或运算得到最终的进位值;

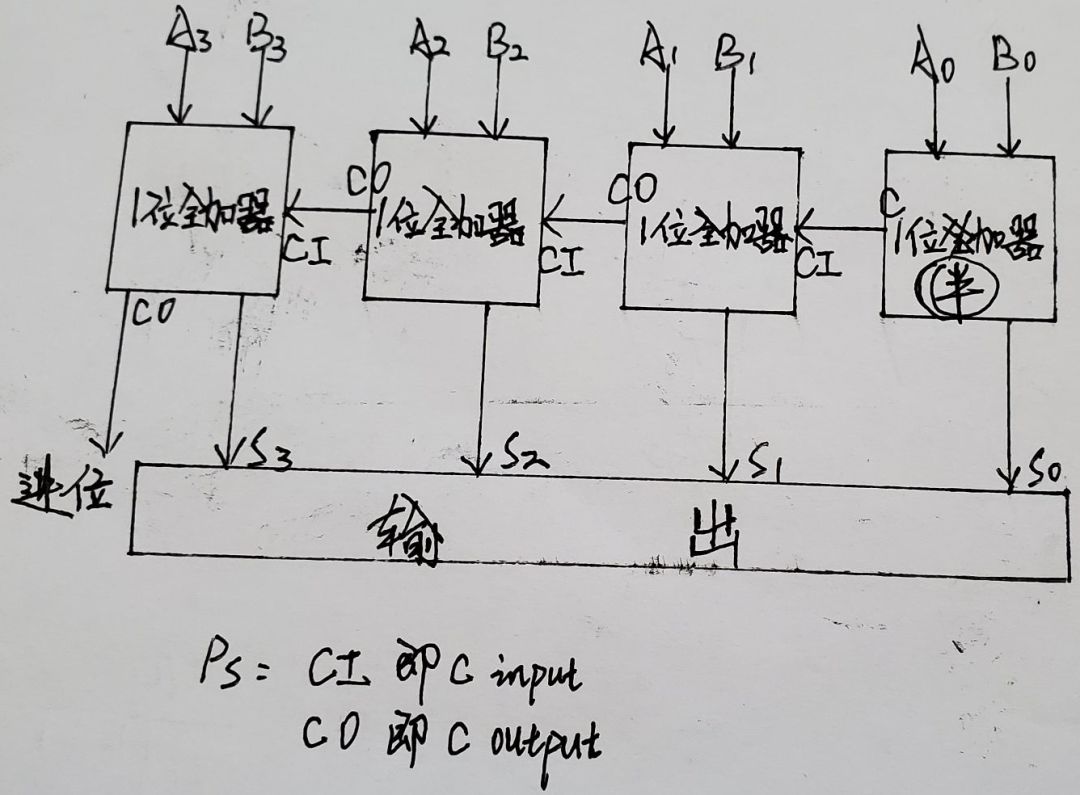

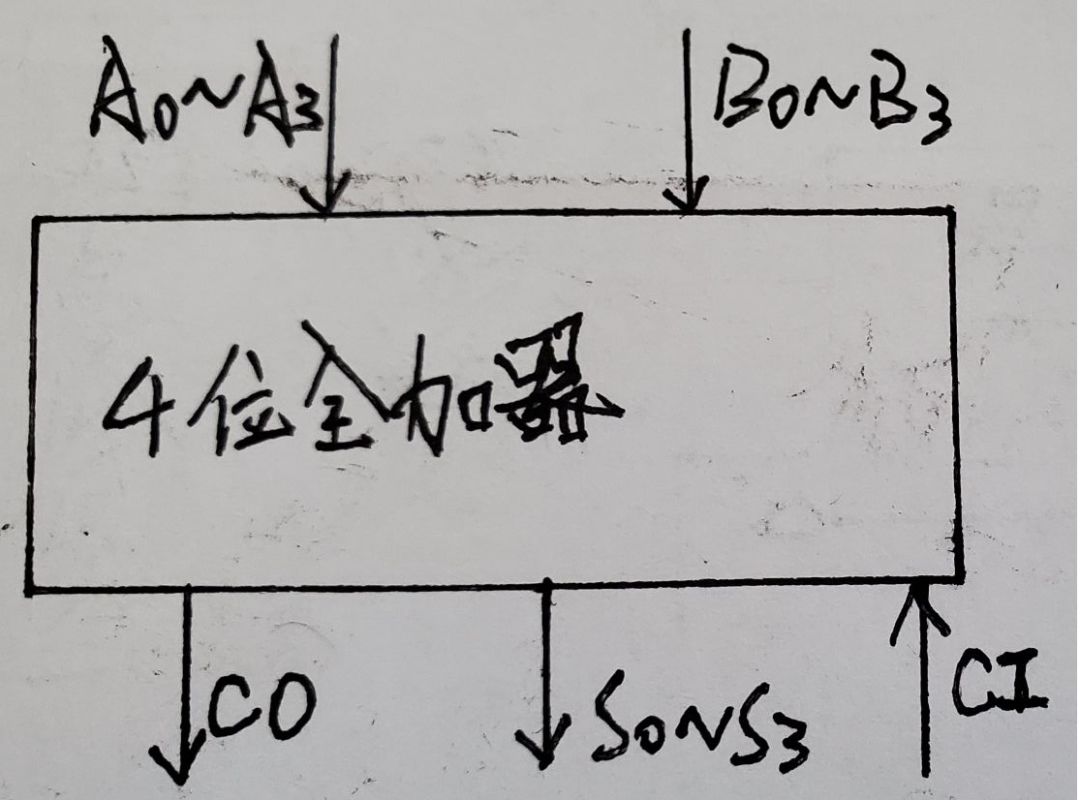

多个一位的全加器串联起来,构成多位全加器,实现多位二进制数的加法运算。

结合下面示意图,帮助你更清楚的理解如何实现多位加法器。

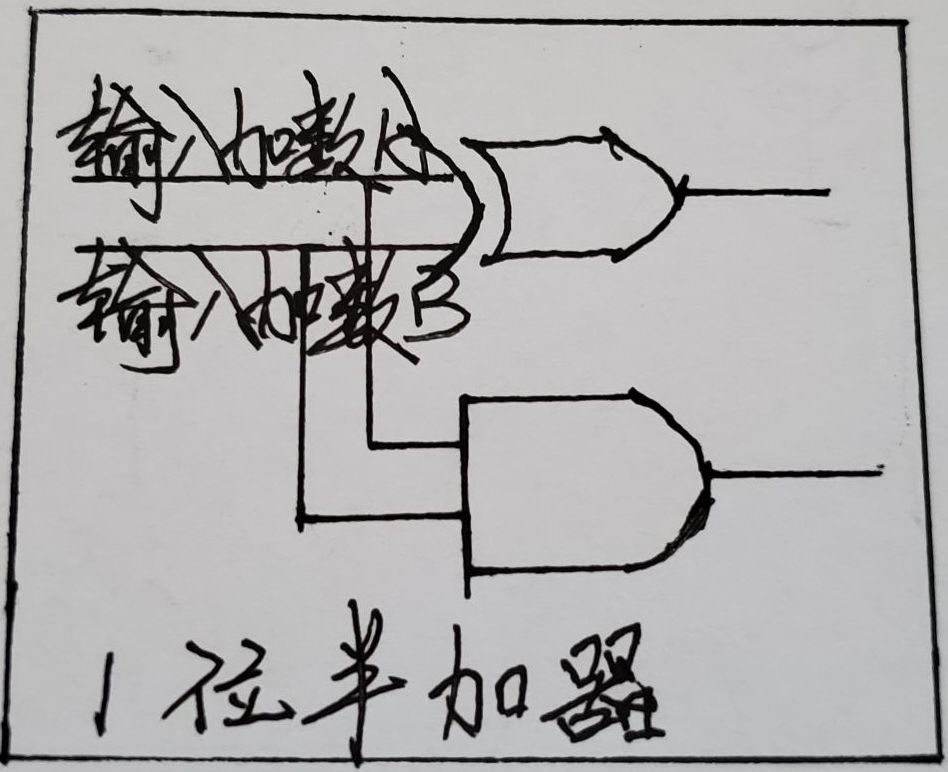

第一层封装:

第二层封装:

第三层封装:

ps:第三层封装最右面加法器没有进位输入,是个半加器。但为了便于扩展、多个加法器串联,现实设计中即使用不到最右侧的进位输入,依然会使用全加器。

ps2:这种加法器并不存在输入顺序,因为每一次开关/输入信号的变化,都会更新输出结果。

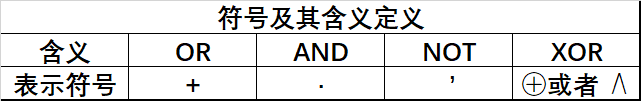

布尔逻辑运算与电路的优化

这种串联开关下,每一个开关状态的变换,都会影响其他开关,进而影响最终的结果。上面只是举例,所以全加器只有四位,而现实中的加法器有着上百个元件,这样的电路会产生很大的电路时延(注意区分时延、延时、延迟这三个说法,搜索引擎简单了解下即可)。所以需要优化逻辑电路的计算时间。

乔治·布尔全面研究和总结了逻辑代数运算的规律,并在1854年出版了The Laws of Thought,介绍和总结了逻辑代数。运用逻辑运算的定律公式,可以借助代数方法快速解决一些用人脑很难判断出的相关性关系。

用1和0作为输入,AND运算结果和乘法的刚好一致,OR不一致,反过来的话两个都不一致 ,故如此定义。

优化

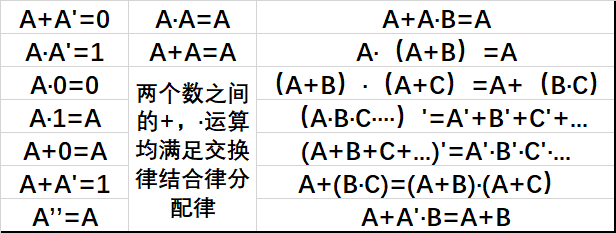

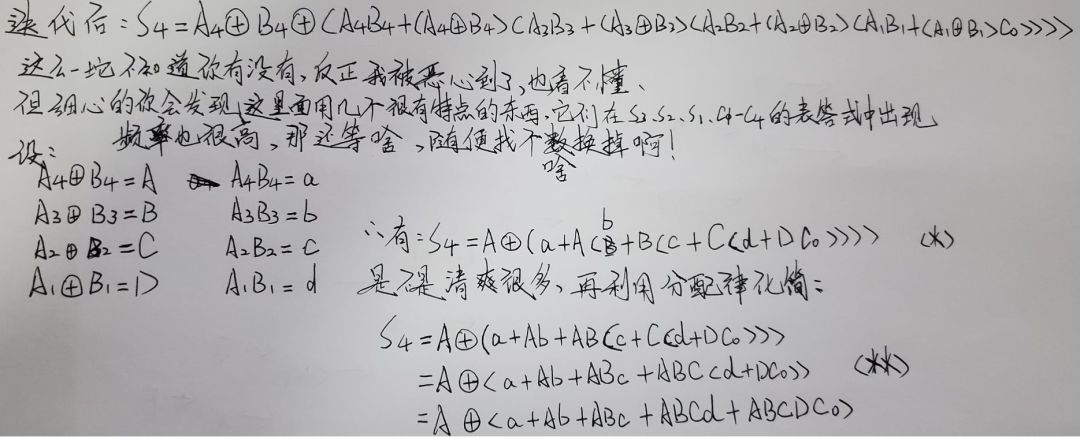

将全加器的输出写成含逻辑运算符的表达式,再将表达式向前迭代,最终整理成只含有原始输入的式子:

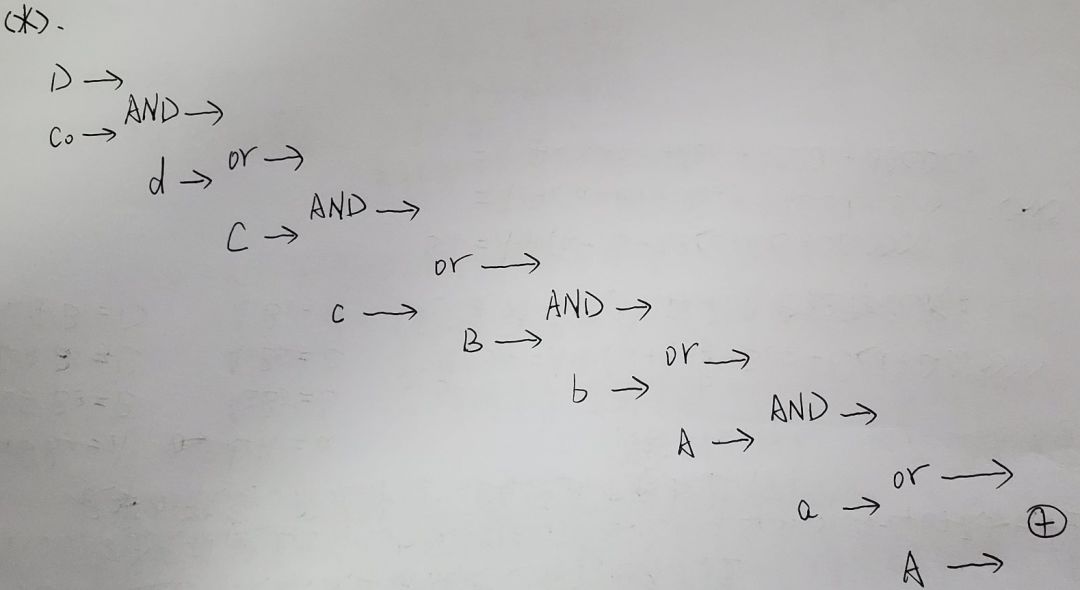

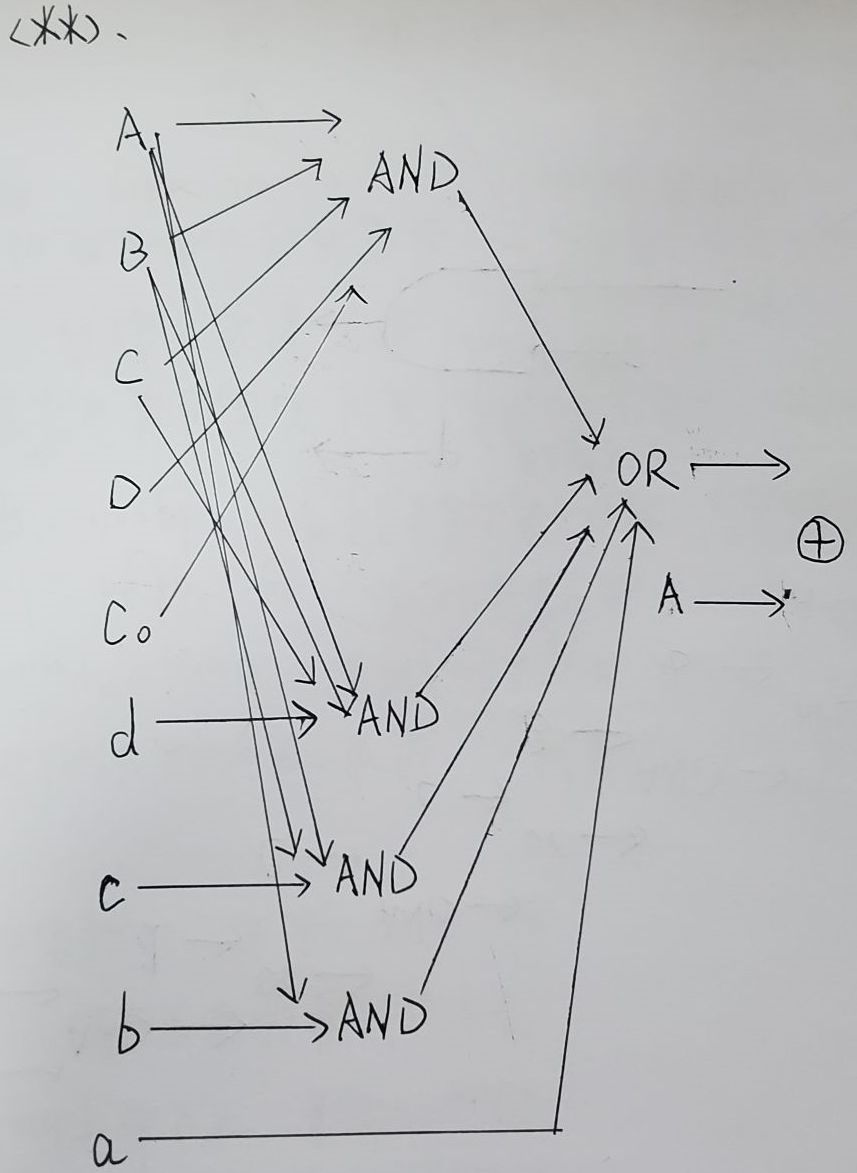

(*)是两个(结果)等效(**)的式子,在实际运算有何区别,我把这两个式子的逻辑电路实现简单的写了下来:

可以看出,(*)基本就是依照前面的4位全加器写出来的,每个门彼此相连串成一串,从左向右传递值。从左往右你每输入一个值要传递好多次才能得到最后结果,不要忘记A~D和a~d也是一次运算,所以这个电路经过了10级才的到结果。

而(**)将个各位的二进制数同时并行计算,各个门之间的依赖性显著降低,只用了4级就得到结果。摆脱了嵌套关系,相互不再依赖。

(*)中的这种串成串的叫串行执行/进位,(**)这种叫并行/先行进位。并行执行是提升计算速度的重要方法之一。

化简后的电路变得面目全非,虽然效果相同,可你从这个电路上已经看不出它执行的是什么逻辑了。但要明确:化简后的电路所显示出来关系使原本就存在的,而不是被创造出来的,只是通过花间消掉了一些看上去被依赖而本质上却毫不相关的项,或者将原本串行执行的逻辑变换为并行。

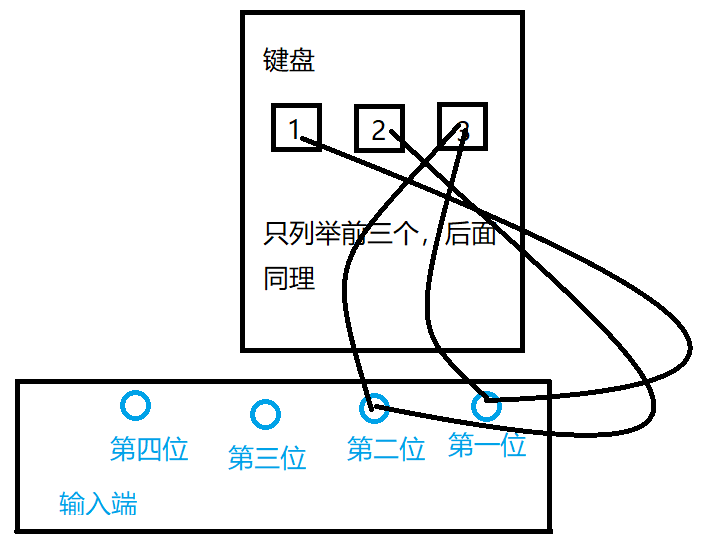

输入端

加法器加的是二进制数,但我们输入要输入十进制,这里简单(复杂的我还不会)说一下10以内正数的输入端设计。

锁存器

一直按着按键不放/持续提供输入信号显然不是我们想要的,这样做很不方便,所以我们希望输入操作结束(恢复低电压)后,之前产生的效果仍能保留下来,即让电路拥有记忆。

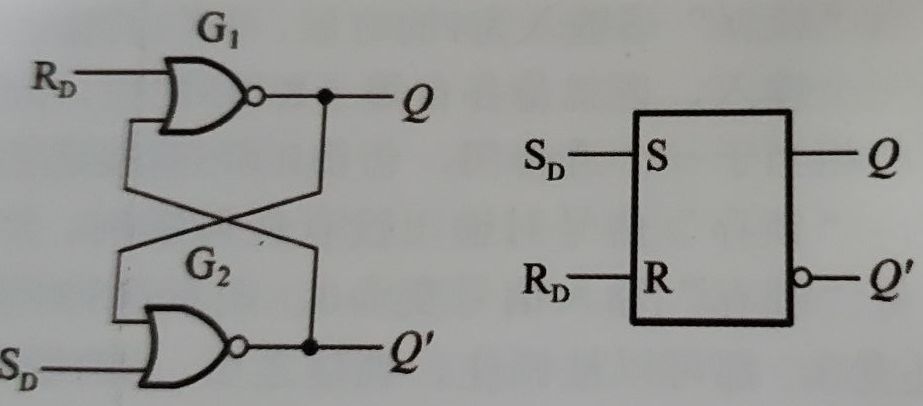

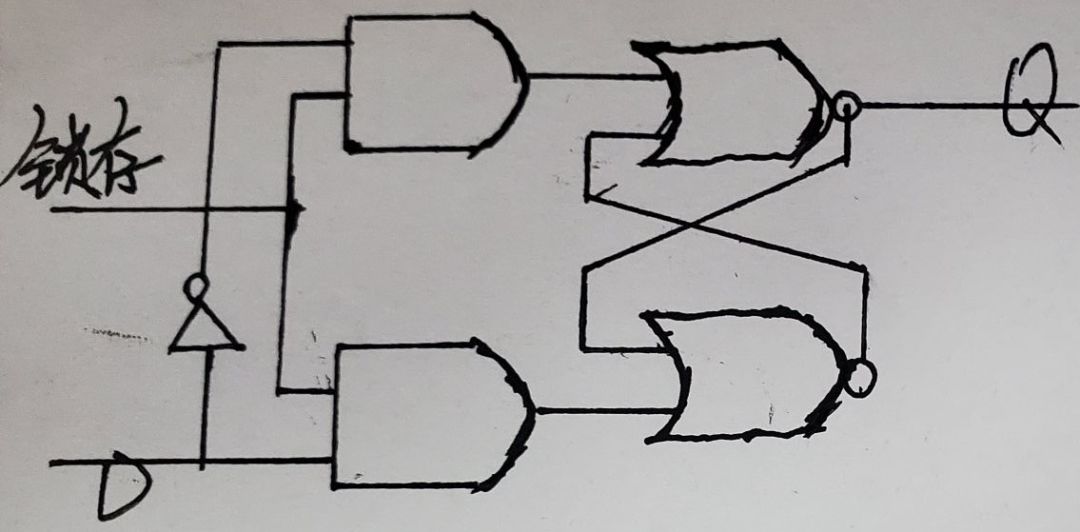

RS触发器

两个或非门按如图方式组合称为RS触发器,这种电路有着奇特的效果:当R为0,S为1时,Q为1,Q'为0,此时S变为0,会发现Q仍然维持原来的状态,还为1,这不正是我们的目标!

S表示Set,R表示Reset(R变时Q会被重置),D表示Data,合称RS触发器。Q'这一输出并没有任何作用,我们选择屏蔽它,R是用来实现锁值的,R的值必须与S相反(为0)。我们这个装置是用来存S的值,R是服务于S,不必关心R值和S值相同(为1)的情况。

这个装置只能实现我们目的的一半:当R为1,S为0的时候,虽然也可以实现Q=S,Q'=P,但这个装置无法维持Q=0。

与门可以用一个输入恒为0来屏蔽另一个输入变化对输出的影响,让输出恒为0,从而使功能完整:

要求RS的值永远为相反关系,没必要两端维持两个独立的输入信号,把要储存值的信号取反输入给原来的R端即可。

储存时,锁存端输入1。经与门处理,与门输出等于另外一个输入,也就是各自等于R和S的值,这时的与门相当于一个穿透门。

输入结束后,锁存输入信号恢复为0。对于第一种(R为0,S为1的)情况,G1输出依然为0,不论G2变成了什么,Q都不会受到影响;对于第二种情况,因为G2输出被锁定为0,锁存变换的一瞬间,G1输出仍为0,即G2输出为1,所以G2可以一直维持0的输出。

此时由于锁存端输入0,不论D输入什么值,Q的值都不会改变,想要储存新的值只有使锁存端再次输入1。如此一来,电路便可储存一位数值,我们称该电路为锁存器。

该装置封装后:

该装置又可被称为D触发器。

该锁存器能够保住一位数据的前提,是在必要出有电源持续供电。

触发器/锁存器这种能够保持事物变化所产生的影响的电路,称为时序逻辑电路,时序逻辑电路的输出值并不一定与输入值联动同步。

有关时序逻辑电路与逻辑的区别很容易理解,这里不做更多赘述,可以通过搜索引擎作进一步了解。