7月16日至18日,第五届RISC-V中国峰会在上海张江科学会堂盛大召开。本次峰会共吸引17个国家的演讲嘉宾和3000余名产业界人士参加。工业和信息化部电子信息司副司长史惠康、RISC-V国际基金会理事长LU DAI、首席执行官Andrea Gallo、SiFive 联合创始人兼首席架构师 Krste Asanović、北京开源芯片研究院首席科学家包云岗等领导和嘉宾出席了本次峰会。

作为大会主单元活动,峰会主论坛于7月17日全天进行。工业和信息化部电子信息司副司长史惠康致辞并指出,RISC-V为中国计算产业提供了良好的发展机遇。一方面,RISC-V是我国掌握处理器核心技术的战略支点,让企业研发人员得以深入参与国际前沿指令集的设计与演进,掌握全流程的技术。另一方面,RISC-V是赋能产业创新的强大引擎,其开源、零授权费、模块化的特性,显著降低了芯片设计的门槛和创新成本,为中国制造提升全球竞争力开辟了新的赛道。此外,RISC-V也是深化国际科技合作的桥梁,是我国首次与全球开发者同步共创核心芯片技术,是提升中国在全球半导体产业中话语权与影响力的宝贵契机。

RISC-V 国际基金会 CEO Andrea Gallo 作了主题为《从指令集架构到产业落地:2025年加速技术进程与RISC-V应用推广》的演讲,他指出 RISC-V 已经成功从嵌入式计算领域延伸至存储技术和高性能计算领域,发展潜力巨大,而中国企业和开发者在其发展进程中扮演着重要且关键的角色,Andrea Gallo在报告中两次提到“香山”高性能处理器,并感谢参与共建 RISC-V 生态的所有企业与工程师,推动了 RISC-V 全球产业的发展。

开芯院首席科学家包云岗也带来了干货满满的名为《关于RISC-V生态建设的几点观察与思考》主旨演讲,他指出,当前 RISC-V 产业落地需迫切解决以下几个问题:

市场缺乏真正富有竞争力的 RISC-V 芯片。芯片产品及解决方案存在“雷声大、雨点小”的问题。

目前要达到“多、快、好、省”的效果, 服务 RISC-V 的工具箱不足3000个,而反观OpenEuler(开源欧拉操作系统)中,X86和ARM的软件包多达30000多个。

从芯片设计、验证、解决方案、技术支持等各个层次的人才都不足,在教学、教学资料、培训、认证等人才培养环节也需要强化改善。

需通过规模化部署 RISC-V 高端芯片案例,如:服务器芯片、AI芯片等,建立行业信心,增加生态影响力。

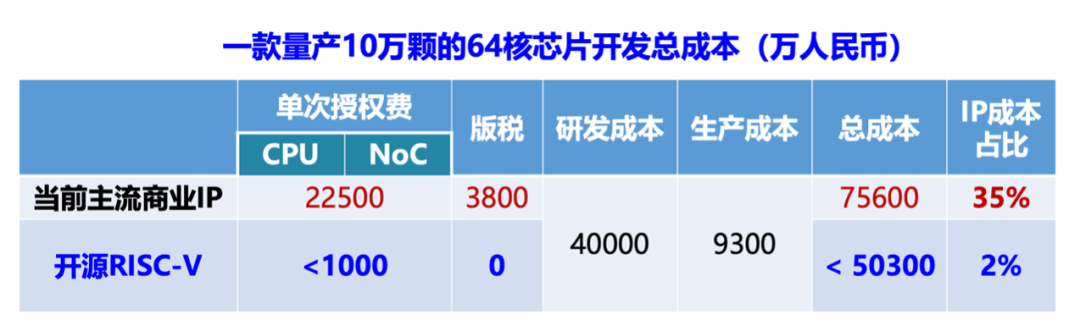

包云岗还提到以RISC-V为代表的开源模式,如何结构性降低芯片开发成本?以研发一款量产10万颗的64核服务器芯片为例,保守估计开发成本约7.5亿元,其中IP授权费用与版税约占35%的成本。基于开源的联合开发模式,可以将单次授权费用降至1000万元以下,将IP成本占比降至2%,为企业节省33%(约2.5亿元)研发费用。这意味着企业可以将更多费用集中到解决方案创新,这是RISC-V带给产业的新机遇。

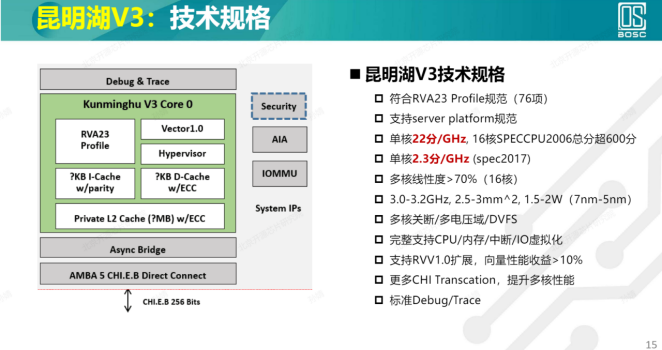

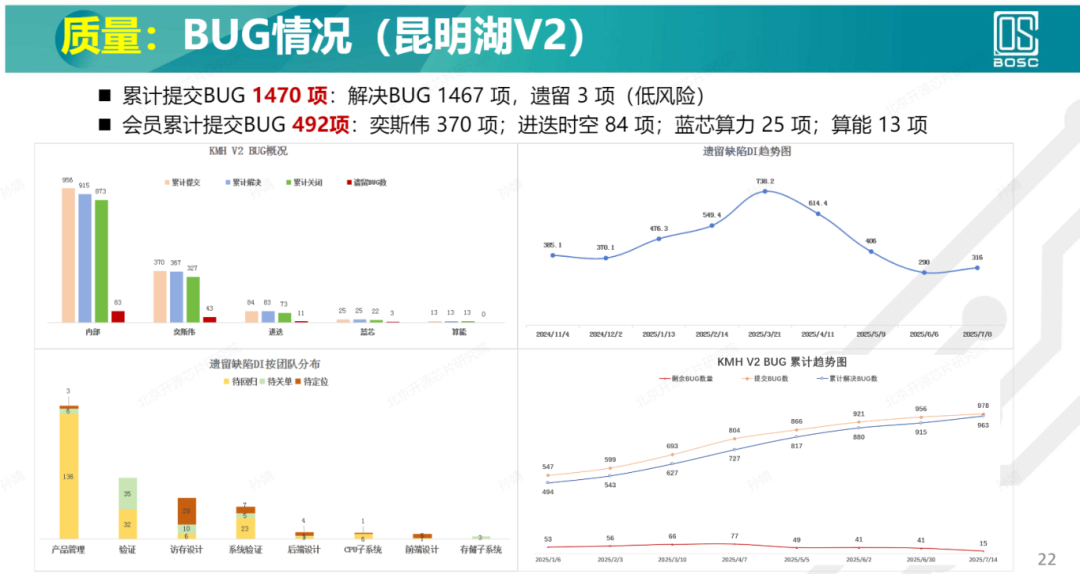

同时,包云岗还分享了”香山“昆明湖 V2的最新进展、发布了昆明湖 V3开发合作伙伴的招募需求。

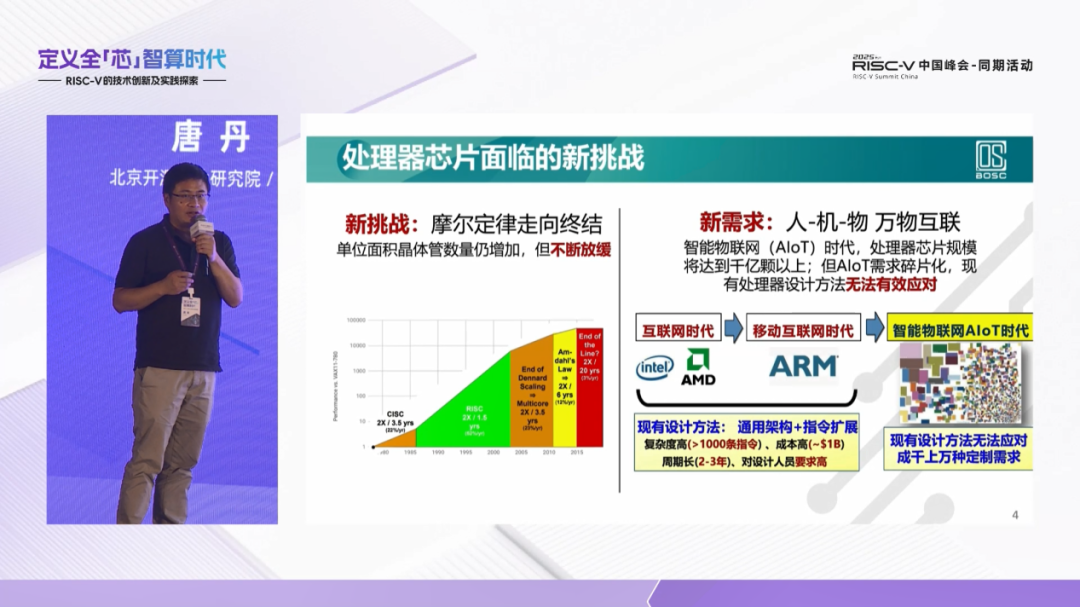

开芯院院长唐丹以《加速推动开源芯片生态发展》为主题围绕开源芯片生态的定义、实践与未来展望展开分享。基于开源模式设计的高性能、高质量芯片可以帮助合作伙伴降低结构性成本,同时开源芯片生态也面临需求碎片化等挑战。唐丹还分享了昆明湖最新进展和开源工具,希望更多合作伙伴共同探索架构、推进开源项目。

本次峰会开芯院工程师团队还参加了7月18日的五个垂直领域分论坛,带来了七场精彩主题分享报告,与线下近千名参会者热情讨论 RISC-V 不同领域下的案例与思考,为 RISC-V 的开放生态注入新鲜动力。

北京开源芯片研究院携汇聚各界力量共同推动的“香山”开源高性能RISC-V处理器核、全球首个开源大规模片上互连网络NoC IP“温榆河”、“开芯云”RISC-V SoC敏捷设计云平台、“万众一芯”开源RISC-V验证平台、“一生一芯”测试芯片及开源 EDA 板卡,以及来自长城汽车、芯动科技、摩尔线程、中科驭数等生态合作伙伴的一系列基于RISC-V的产品亮相会场,吸引众多专业人士驻足交流。

2025年 RISC-V 中国峰会圆满结束,开芯院将继续秉持“携手共进,共建生态”的理念与大家下次再见。