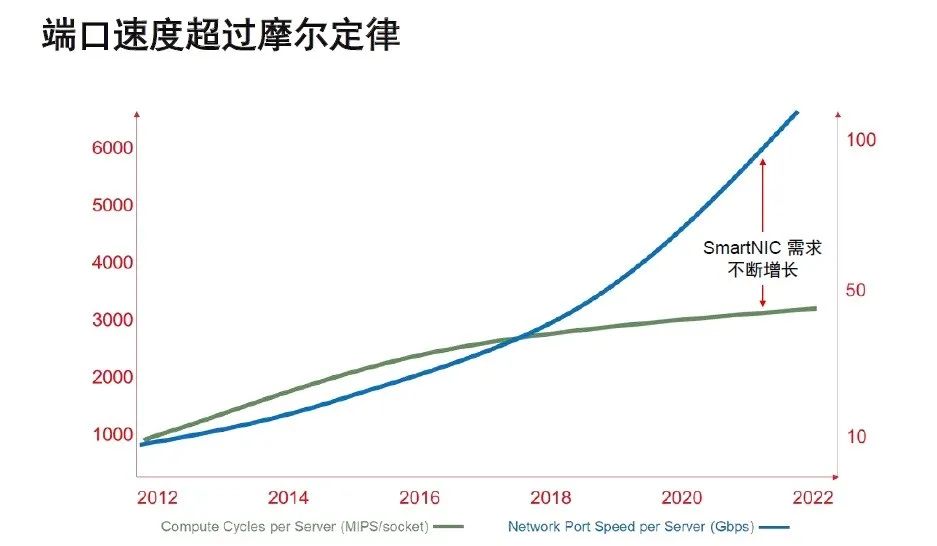

CPU不能承受之重

图1 端口速度超过摩尔定律

数字基础设施中的新物种

DPU发展仍在早期,强调落地和生态打造。数据中心核心算力芯片仍以CPU、GPU、FPGA和少量ASIC为主,并且通用CPU还是占据绝对统治地位。和CPU、GPU一样,DPU作为基础层的应用支撑,发展的关键是必须重视生态建设和应用支撑,落地并抢占市场、营造生态才是DPU产业发展的关键所在。

Intel、Marvell、NVIDIA成为最有潜力的产业先驱。大多数DPU方案是从基本的网络控制器开始扩展至SoC。就Intel而言,其产品采取处理器配合FPGA,外加加速引擎的方式;Marvell则采取使用最新处理器内核配合加速引擎的方式;NVIDIA则采用了处理器配合ASIC,外加加速引擎的方式。这三种方式代表着DPU产业的未来主流的发展方向。

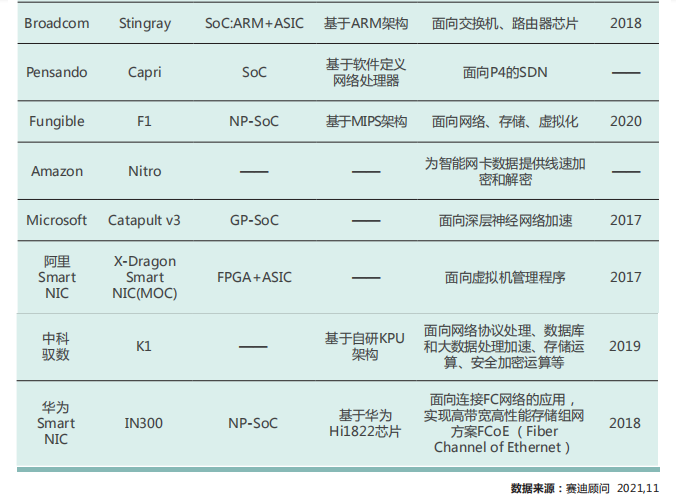

目前DPU市场仍处于蓝海,呈现百家争鸣的竞争格局。Intel、NVIDIA等企业纷纷布局DPU产业,同时包括AWS、阿里巴巴、华为在内的各大云服务商,都已经在布局自己的云端处理器,行业竞争格局分析如下:

DPU方案类型大致可以概括为三种:

一是以通用众核处理器为基础DPU,例如Broadcom的Stingray架构,以多核ARM为核心,以众取胜,可编程灵活性较好,但是应用针对性不够,对于特殊算法和应用的支持,与通用CPU相比并无太显著优势;

二是以专用核为基础的异构核阵列,这种架构的特点是针对性较强、性能较好,但是牺牲了部分灵活性,如IPU;

第三种路线是结合了前面二者优势,即将通用处理器的可编程灵活性与专用的加速引擎相结合,正在成为最新的产品趋势,以NVIDIA的BlueField-3系列DPU来看,就包括16个ARM核及多个专用加速引擎,Fungible的DPU则包含6大类的专用核,和52个MIPS小型通用核。

随着DPU将数据中心的基础设施操作从CPU上卸载过来,数据中心将形成DPU、GPU、CPU三位一体的状态;NVIDIA通过收购Mellanox积极布局DPU,抢占市场,凭借在GPU的绝对优势以及未来DPU的发力,NVIDIA有望在服务器处理器三大芯片中占据其二。对各厂商及现有产品分别综述如下:

在技术路线上,英伟达DPU基于所收购的Mellanox网络方案及ARM架构实现,侧重于数据安全、网络、存储卸载。

在2021年6月15日的Six Five峰会上,英特尔推出了全新的基础设施处理器(IPU,全称Infrastructure Processing Unit)。IPU是一个网络设备,可以安全地加速和管理数据中心的基础设施功能与可编程硬件,旨在使云和通信服务提供商减少在中央处理器方面的开销,并充分释放性能价值。利用IPU,客户能够部署安全稳定且可编程的解决方案,从而更好地利用资源,平衡数据处理与存储的工作负载。IPU可将CPU或xPU连接到网络,加速主机基础设施功能,并适用于现有和新兴基础设施用例,包括安全性、虚拟化、存储、负载平衡,以及虚拟网络功能和微服务的数据路径优化。IPU增强了基础NIC中丰富的以太网网络功能,通过高度优化的硬件加速器和紧密耦合的计算引擎的组合处理任务来实现加速。适应性是通过标准且易于使用的编程框架实现的,该框架结合了硬件和软件功能。IPU扩展了英特尔的智能网卡功能,旨在应对当下复杂的数据中心,并提升效率。

凭借在数据中心领域多年的耕耘与积淀,深谙数据中心企业需求并洞察行业发展的英特尔,IPU产品从设计、生产到推出,每一步都能看到合作伙伴的身影。当前基于Intel FPGA的IPU已经导入多个云端服务商,目前也着手测试第一款采用ASIC的IPU产品;

Intel也强调接下来将会推出更多基于FPGA的IPU与专用ASIC,为新世代资料中心带来更具弹性、安全与效率的XPU架构。在适用于企业和云的IPU阵营,使用英特尔FPGA实现数据中心加速面向云服务提供商的采用英特尔FPGA的IPU有助于充分利用网络功能并帮助提高基础设施投资的收入;英特尔IPU为VMware下一代基础架构提供动力英特尔技术使VMware能够为客户提供对虚拟机、容器和裸机环境的统一管理;Monterey项目则重新定义混合云架构,英特尔IPU创新为边缘节点、网络基础设施和数据中心计算提供了更高的性能。

Xilinx的开发是基于FPGA的Smart NIC,Xilinx于2019年秋季收购了Solarflare Communications,Solarflare自2012年以来一直在构建基于ASIC和FPGA的NIC进行电子交易。

Xilinx的Alveo U25将双SFP28端口直接连接到Zynq系列芯片,包括6GB DDR4内存,Zynq的FPGA和ARM内核可通过该芯片上运行的程序对其进行访问。FPGA有520K逻辑元件可用,但是提供的四核ARM可以弥补可用门数的减少。Xilinx将Alveo U25推向市场,最初是针对那些要求开放虚拟交换机(OvS)卸载功能的客户。其将增加IPsec、机器学习(ML)、深度包检查(DPI)、视频转码和分析等功能的卸载。

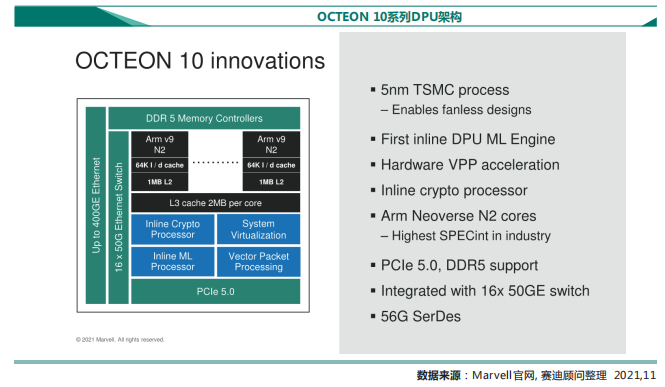

Marvell最新推出的OCTEON 10系列DPU采用了台积电5nm制程工艺,且首次用上了ARM的Neoverse N2 CPU内核。这种类型的多功能芯片,旨在帮助移动和处理那些通过网络传输的数据,可实现集成机器学习推理的引擎、Inline加密处理引擎、以及矢量数据包处理器等的虚拟化。OCTEON 10也是Marvell首款采用台积电N5P工艺制造的DPU芯片。其不仅率先集成了ARM的Neoverse N2 CPU核心,还支持最新的PCIe 5.0 I/O与DDR5内存。

受益于最新的ARM处理器内核,OCTEON 10在整型处理上是目前算力最高的DPU,然而其浮点运算仅支持FP16,在做内联机器学习时有一定局限性。OCTEON 10 新系列引入了矢量数据包处理引擎(VPP),与当前一代的标量处理引擎相比,它能够将数据包的处理吞吐量,大幅提升至 5 倍。

中科驭数的创始团队主要来自中科院计算所计算机体系结构国家重点实验室,是中国最早进行DPU芯片研发的团队之一。中科驭数提出了软件定义加速器技术(Software Defined Accelerator),自主研发了KPU(Kernel Processing Unit)芯片架构,并于2019年设计出业界首颗数据库与时序数据处理融合加速芯片,已经成功流片。中科驭数的DPU芯片,正是基于自研的KPU芯片架构,具有网络协议处理、数据库和大数据处理加速、存储运算、安全加密运算等核心功能。

来源:智能计算芯世界

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术总结请参考“架构师全店铺技术资料打包”相关电子书(37本技术资料打包汇总详情可通过“阅读原文”获取)。

内容持续更新,现下单“全店铺技术资料打包(全)”,后续可享全店更新“免费”赠阅,价格仅收198元(原总价350元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“IT技术全店资料打包汇总(全)”电子书资料详情。