点击上方蓝字【囧囧妹】一起学习,一起成长!

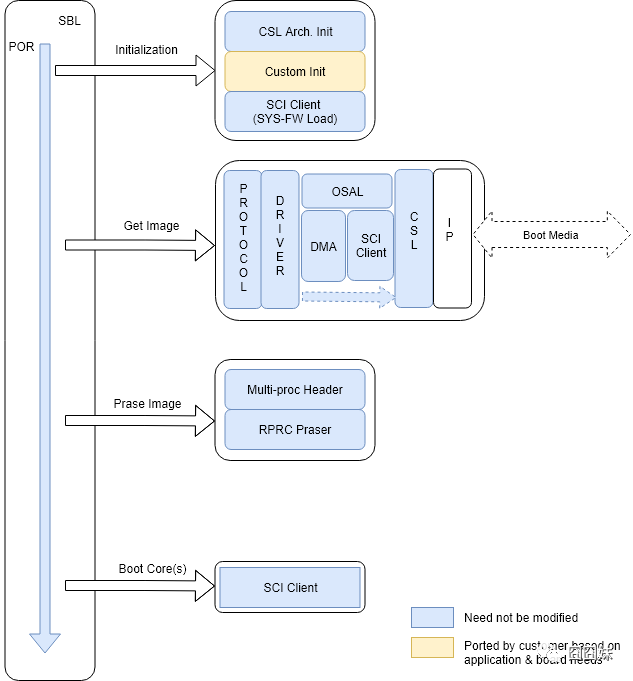

一、SBL框图

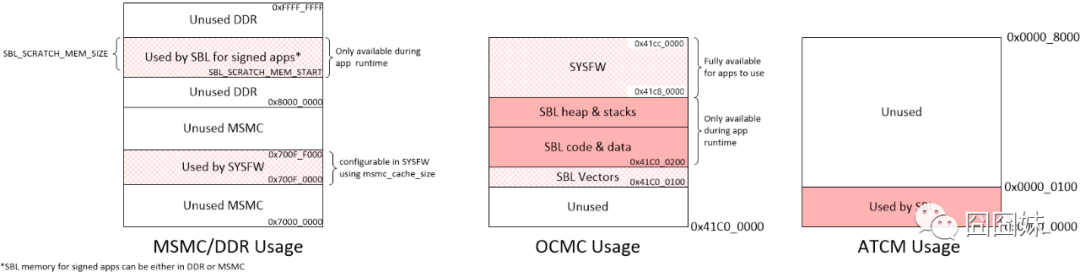

二、内存映射

sbl│├── board│ └── k3│ └── sbl_main.c <= define main() for SBL, board specific init│├── build│ ├── makefile <= makefile for the SBL component│ ├── sbl_am65xx.sh <= For legacy, called by Yocto build│ ├── sbl_boot_test.mk <= Builds SBL single core tests│ ├── sbl_smp_test.mk <= Builds example app for using SBL lib│ ├── sbl_mcu0_boot_perf_test.mk <= Builds example app for SBL performance tuning│ ├── sbl_mcu0_boot_xip_entry.mk <= Builds example trampoline app to demonstrate transitioning to a XIP app from SBL│ ├── sbl_mcu0_boot_xip_test.mk <= Builds example app to demonstrate XIP execution from XIP capable boot media│ ├── sbl_img.mk <= builds SBL image that is loaded and executed by ROM code│ ├── sbl_lib.mk <= Builds sbl library that other apps can link into│ ├── sbl_multicore_smp.mk <= Builds multi-core image from SBL lib eg. test to demonstrate symmetric multiprocessor boot (SMP)│ └── sbl_multicore_amp.mk <= Builds multi-core image from single core tests to demonstrate asymmetric multiprocessor boot (AMP)│├── example│ └── k3MulticoreApp│ ├── binary│ │ └── [soc]│ │ ├── sbl_baremetal_*.appimage <= SBL loadable board specific sample apps for testing SBL boot flow on GP devices│ │ ├── sbl_baremetal_*.appimage.signed <= SBL loadable board specific signed sample apps for testing SBL boot flow on HS devices│ │ └── sbl_baremetal_*_release.x*.bin <= Binary image that can be eXecuted In Place on XIP capable boot media| ├── [soc]│ │ ├── mcuAmplinker.lds <= Linker command file when TI CGT is used for Asym. Multiproc. boot│ │ ├── mpuAmplinker.lds <= GCC linker command file (for Cortex Axx cores) for Asym. Multiproc. boot│ │ ├── mcuXiplinker.lds <= Linker command file for XIP trampoline app│ │ └── xip_entry.lds <= Linker command file for XIP test case│ ├── mcuBootPerfLinker_j7.lds <= TI CGT Linker command file for SBL performance tuning example (J721E)│ ├── mcuBootPerfLinker.lds <= TI CGT Linker command file for SBL performance tuning example (AM65xx)| ├── mcuBootPerfLinker_small.lds <= TI CGT Linker command file for SBL performance tuning example (for boot with MCU domain only)│ ├── mcu[core#]LockStepLinker.lds <= Linker command file when TI CGT is used for R5 lock-step boot│ ├── mpuSmplinker.lds <= GCC linker command file (for Cortex Axx cores) for SMP boot│ ├── xip_entry.asm <= Entry point of XIP trampoline app│ ├── xip_stub.c <= Simple SBL test app that demonstrates transitioning to a XIP app│ ├── sbl_amp_multicore.c <= Simple SBL test that displays UART message│ ├── sbl_amp_multicore_sections.h <= Allows same source to be loaded to different sections for different cores.│ ├── sbl_mcu_0_boot_perf_benchmark.c <= SBL Test to tune boot performance.│ ├── sbl_multicore_a53.asm <= Test case entry point for Cortex-Axx cores│ ├── sbl_multicore_r5.asm <= Test case entry point for Cortex-R5 cores│ ├── sbl_multicore_r5_sections.inc <= Allows same source to be loaded to different sections for different MCUs.│ ├── sbl_printf.c <= Lightweight UART printf function for SBL testing│ ├── sbl_smp_multicore.c <= Simple SBL SMP test that uses SBL lib to reset MPUs│ └── sbl_smp_r5.asm <= Provides dummy override function for __mpu_init for SMP testcase.│├── binary <= ROM bootable SBL images for each board/boot media│ ├── [board]│ └── [bootmedia]│ └── bin│ └── sbl_[bootmedia]_img_mcu1_0_release.tiimage│├── lib <= SBL lib for each boot media/board supported│ ├── [bootmedia]│ │ └── [board]│ │ └── r5f│ │ └── release│ │ └── sbl_lib_[bootmedia].aer5f│ └── cust│ └── [board]│ └── r5f│ └── release│ └── sbl_lib_cust.aer5f│├── soc <= SOC specific SBL code│ └── k3│ ├── [soc]| | └── linker.cmd <= Linker file used for generating ROM loadable SBL image.│ ├── sbl_err_trap.h <= Error loops for SBL│ ├── sbl_init.asm <= SBL Entry point│ ├── sbl_misc.asm <= SBL Assembly utility functions│ ├── sbl_log.h <= SBL logging framework│ ├── sbl_sci_client.c <= Calls system firmware on DMSC│ ├── sbl_sci_client.h│ ├── sbl_slave_core_boot.c <= Code that contains the sequence to release a core from reset│ ├── sbl_slave_core_boot.h│ ├── sbl_soc.c <= Cache Ops, PMU init, image verfication, etc & SoC specific code like RAT Init..│ ├── sbl_soc_cfg.h <= Abstraction layer for hiding SoC level changes from SBL│ └── sbl_profile.h <= SBL profiling framework│├── src <= Common drivers used across SOCs│ ├── mmcsd│ ├── hyperflash│ ├── ospi│ ├── qspi│ ├── uart│ ├── rprc <= RPRC image parser used by SBL│ └── spi│└── tools├── btoccs├── byteswap├── ccsutil├── combined_appimage <= Creates a "combined" .appimage file for booting HLOS images (e.g., ATF,U-boot,Linux)│ ├── bin│ │ └── [board]│ │ ├── base-board.dtb <= Default (example) Linux DTB per platform - to be replaced with desired DTB│ │ └── combined.appimage <= Output "combined" .appimage for HLOS + RTOS images boot (after build)│ ├── config.mk <= Configuration make include file. Use this to specify images to include in combined.appimage│ └── makefile <= combined.appimage Makefile├── flashWriter <= Unused for AM65xx/J721E. AM65xx/J721E uses Uniflash to program flashes.├── multicoreImageGen <= Stitches multiple RPRC images for different cores into a single image├── omapl13x_boot_utils <= Unused for AM65xx/J721E├── omapl13x_sd_card_format <= Unused for AM65xx/J721E├── out2rprc <= Converts .out into .rprc files, so that SBL can load non-continuous memory sections├── scripts <= Scripts used by .out generated by CCS projects into SBL loadable images│ ├── K3ImageGen.bat│ └── K3ImageGen.sh└── tiImageGen <= Unused for AM65xx/J721E. Image generation is handled by PDK build framework (<sdk_install_path>/pdk_*/packages/ti/build/)

| 抵消 | 二进制值 |

|---|---|

| 0x00000000 | 魔数(43525052) |

| 0x00000004 | 入口点(位置) |

| 0x00000008 | 预留地址 |

| 0x0000000C | section数量 |

| 0x00000010 | 版本 |

| 抵消 | 二进制值 |

|---|---|

| 0x00000000 | 段起始地址 |

| 0x00000004 | 预留地址 |

| 0x00000008 | 大小 |

| 0x0000000C | 预留的 CRC |

| 0x00000010 | 预留 |

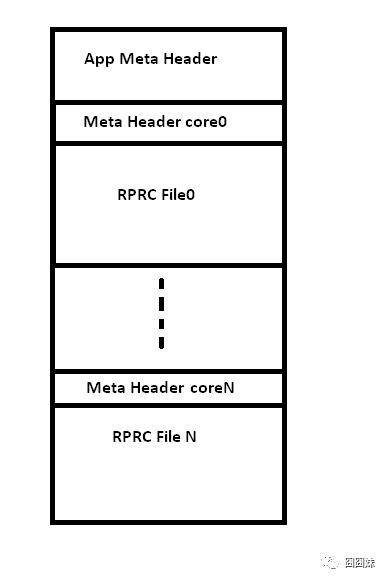

多核启动镜像格式

meta的头部起始

| 偏移 | 二进制值 |

|---|---|

| 0x00000000 | 魔数字符串 (0x5254534D) |

| 0x00000004 | 文件数 |

| 0x00000008 | 设备ID |

| 0x0000000C | 预留 |

每个核的meta首部

| 偏移 | 二进制值 |

|---|---|

| 0x00000000 | 核id |

| 0x00000004 | 镜像偏移 |

文章转载自囧囧妹,如果涉嫌侵权,请发送邮件至:contact@modb.pro进行举报,并提供相关证据,一经查实,墨天轮将立刻删除相关内容。