3

软考《数据库系统工程师》地铁复习笔记.pdf

100墨值下载

说明:

此文档系我在备考 2024 年软考中级数据库系统工程师的时候,在复习国家的官方教

材,历年真题和部分其他参考复习资料时,随手所做的复习笔记,后来也修正了一些内容。

我的这份笔记你可以参考,但不要迷恋,你应该自己从头再写一遍适合自己的,因为每个

人都有适合自己的复习笔记。在程序员的眼中,除了自己写的代码,其它的都是垃圾,DBA

的眼中各种各样的笔记代码同样如此。各位 DBA 们,战斗起来吧!这场考试,你将被狠狠

的虐待,但也将获得新生!

(注意:此笔记不保证所有知识点 100%的正确性,毕竟我也不是专业的老师,更不是神,

希望你能发现错误并自己纠正,但这份笔记带给我的基础科成绩是 66 分。呕心沥血原创笔

记,不喜勿喷,一经下载,概不退货,慎重下载,只赚墨值,禁止用于赚 RMB,太不仗义

了。为啥叫地铁复习笔记,因为临考的最后几天,我把他打印下来然后在上下班的地铁上

拿着它不停的看,非常合适,我建议你也这么做。)

第一章 计算机系统知识

1. 计算机基本硬件: 运算器,控制器,存储器,输入设备、输出设备

2. CPU 组成:运算器,控制器,寄存器,内部总线

运算器:

算术逻辑单元(ALU),累加寄存器(AC,用于暂存操作数和运算结果,比如程序中的

源操作数)

数据缓冲器寄存器(DR, 暂存由内存读入的指令或数据,就是 CPU 缓存)

状态条件寄存器(PSW, 保存算术指令和逻辑指令运行的结果状态,比如进位)

控制器: 指令寄存器(IR, 缓存指令),程序计数器(PC,生成下一条指令地址,CPU

中它首先被操作),地址寄存器(AR,保存当前 CPU 所访问内存单元的地址),指令译码

器(ID,含操作码和地址码,主要对操作码进行翻译)

中断向量表用来保存各个中断源程序的入口地址。

计算机操作的最小是的单位是时钟周期。

CPU 发出的数据地址都是实际的主存物理地址。

CPU 只与内存交流,高速缓存用于缓解内存与 CPU 之间的速度不匹配。

3. 总线:

数据总线:与存储器的字长数相等,表示一次计算可以传送的数据位数。

地址总线:与存储器有多少个存储单元相等(实际上是与刚好满足 2^n >= 存储单元数

量中的最小 n 相等。)

比如: 16K x 32 的存储器,表示总共有 16K(M,K,B 之间由 1024 进位)个存储单元,

每个存储单元字长 32 位。 数据线数量等于 32, 16k 个存储单元=16x1024 bytes = 2^14 次

方,因此地址总线为 14 根。

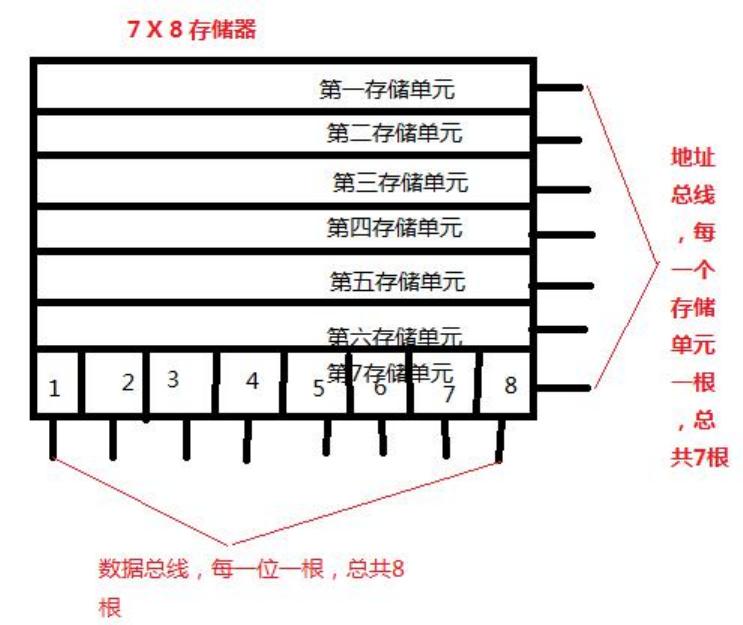

数据线和地址线关系如图:

注意:此图只是用于比较形象的说明什么是数据总线,什么是地址总线,并非就是说每

一个存储单元就需要一根地址总线,地址总线的数量为刚好满足 “2^n >= 存储单元数量”

中的最小 n 相等。比如这里的 7 个存储单元,满足的 n 值为 3,那么地址总线的数量实际上

是 3 根。地址总线的设计核心,就是用二进制编码来表示存储单元的地址,那么解答时只

需要弄清楚至少需要多少位二进制才能表示出这么多个存储单元就可以了,通常就是 2 的多

少次方。

总线带宽=总线工作频率 X 总线位宽

总线位宽:总线能同时传送的二进制数据的位数,或者指数据总线的位数

总线工作评率:以 MHz 为单位

4. 存储器相关知识

一个字节= 1Byte = 8 bit , 一个字=4 个字节,注意存储带宽单位 Mb/s 与 MB/s 的区别,

前者以位为单位,后者以字节为单位

存储存取时间,就是一次存取需要花费的时间

存储周期,指相邻两次存取之间的时间

存储器带宽,指一秒内能访问的数据位数。

比如,一个存储周期为 500ns,每次周期访问 4 字节的存储器,其带宽计算为:

1s=1000ms=1000,000 微秒=1000,000,000ns

1000,1000,1000/500=2000,000 个周期

存储器带宽=2000,000 X 4 字节=8000,000 字节= 8000,000 X 8 位=64000,000 位 = 64Mb/s

一个 16K x 8 的存储器:表示这个存储器里面有 16k 个存储单元,每个存储单元就是 8 位,

of 69

100墨值下载

【版权声明】本文为墨天轮用户原创内容,转载时必须标注文档的来源(墨天轮),文档链接,文档作者等基本信息,否则作者和墨天轮有权追究责任。如果您发现墨天轮中有涉嫌抄袭或者侵权的内容,欢迎发送邮件至:contact@modb.pro进行举报,并提供相关证据,一经查实,墨天轮将立刻删除相关内容。

下载排行榜

评论